| Verilog Operator | Name                                                                           | Functional Group  |

|------------------|--------------------------------------------------------------------------------|-------------------|

| > >= < <=        | greater than greater<br>than or equal to less<br>than less than or equal<br>to | relational        |

| == !=            | case equality case<br>inequality                                               | equality          |

| & ^              | bit-wise AND bit-wise<br>XOR bit-wise OR                                       | bit-wise bit-wise |

| &&               | logical AND logical<br>OR                                                      | logical           |

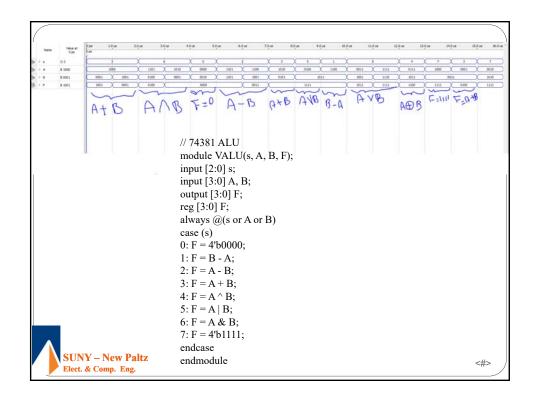

| Design of an ALU using Case<br>Statement |                                         | // 74381 ALU<br>module alu(s, A, B, F);<br>input [2:0] s;<br>input [3:0] A, B; |  |                                               |

|------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------|--|-----------------------------------------------|

|                                          | S                                       | Function                                                                       |  | output [3:0] F;                               |

|                                          | 0                                       | Clear                                                                          |  | $\operatorname{reg}\left[3:0\right]F;$        |

|                                          | 1                                       | B-A                                                                            |  | always @(s or A or B)                         |

|                                          | 2                                       | A-B                                                                            |  | case (s)                                      |

|                                          | 3                                       | A+B                                                                            |  | 0: F = 4'b0000;                               |

|                                          | 4                                       | A XOR B                                                                        |  | $1: \mathbf{F} = \mathbf{B} - \mathbf{A};$    |

|                                          | 5                                       | A OR B                                                                         |  | $2: \mathbf{F} = \mathbf{A} - \mathbf{B};$    |

|                                          | 6                                       | A AND B                                                                        |  | 3: F = A + B;                                 |

|                                          | 7                                       | Set to all 1's                                                                 |  | $4: F = A \wedge B;$                          |

|                                          |                                         |                                                                                |  | $5: \mathbf{F} = \mathbf{A} \mid \mathbf{B};$ |

|                                          |                                         |                                                                                |  | 6: F = A & B;                                 |

| 1988                                     |                                         |                                                                                |  | 7: F = 4'b1111;                               |

|                                          | Now F                                   | Poltz                                                                          |  | endcase                                       |

|                                          | SUNY – New Paltz<br>Elect. & Comp. Eng. |                                                                                |  | endmodule                                     |

```

4-bit Shift Register with Reset

module srg_4_r_v (CLK, RESET, SI, Q,SO);

input CLK, RESET, SI;

output [3:0] Q;

output SO;

reg [3:0] Q;

assign SO = Q[3];

always@(posedge CLK or posedge RESET) begin

if (RESET)

Q <= 4'b0000;

else

Q \le \{Q[2:0], SI\};

end

endmodule

SUNY – New Paltz

Elect. & Comp. Eng.

```

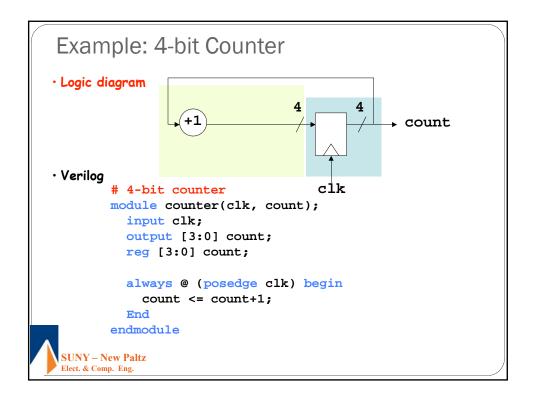

# 4-bit Binary Counter with Reset

```

module count_4_r_v (CLK, RESET, EN, Q, CO);

input CLK, RESET, EN;

output [3:0] Q;

output CO;

reg [3:0] Q;

assign CO = (count == 4'b1111 && EN == 1'b1) ? 1 : 0;

always@(posedge CLK or posedge RESET)

begin

if (RESET)

Q <= 4'b0000;

else if (EN)

Q <= Q + 4'b0001;

end

endmodule

SUNY - New Paltz

Elect. & Comp. Eng.

```

| Verilog                            |                                   | Functional    | Verilog  | Name                  | Functional  |

|------------------------------------|-----------------------------------|---------------|----------|-----------------------|-------------|

| Operator                           |                                   | Group         | Operator |                       | Group       |

| []                                 | bit-select or part-               |               | +        | binary plus           | arithmetic  |

|                                    | select                            |               | -        | binary minus          | arithmetic  |

| ()                                 | parenthesis                       |               | <<       | shift left            | shift       |

| !                                  | logical negation                  | logical       | >>       | shift right           | shift       |

| ~                                  | negation                          | bit-wise      | >        | greater than          | relational  |

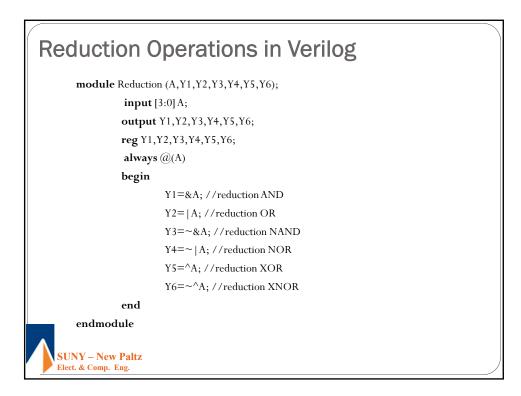

| &                                  | reduction AND                     | reduction     | >=       | greater than or equal | relational  |

|                                    | reduction OR                      | reduction     | <        | to                    | relational  |

| $\sim \&$                          | reduction NAND                    | reduction     | <=       | less than             | relational  |

| ~                                  | reduction NOR                     | reduction     |          | less than or equal to |             |

| ^                                  | reduction XOR                     | reduction     | ==       | case equality         | equality    |

| $\sim^{\wedge}$ or $^{\wedge}\sim$ | reduction XNOR                    | reduction     | !=       | case inequality       | equality    |

| +                                  | unary (sign) plus                 | arithmetic    | &        | bit-wise AND          | bit-wise    |

| -                                  | unary (sign) minus                | arithmetic    | ^        | bit-wise XOR          | bit-wise    |

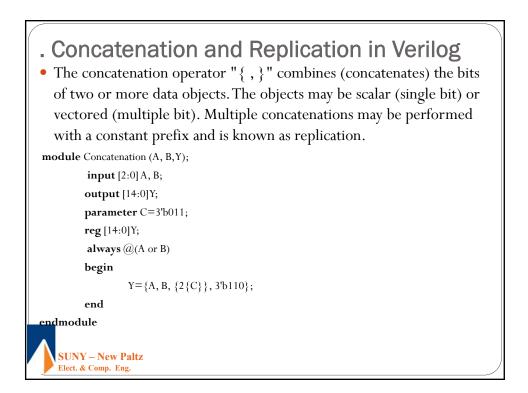

| { }                                | concatenation                     | concatenation |          | bit-wise OR           | bit-wise    |

| {{}}                               | replication                       | replication   | &&       | logical AND           | logical     |

| *                                  | multiply                          | arithmetic    |          | logical OR            | logical     |

| /                                  | divide                            | arithmetic    | ?:       | conditional           | conditional |

| %                                  | modulus                           | arithmetic    |          |                       |             |

|                                    | NY – New Paltz<br>t. & Comp. Eng. |               | -        |                       |             |

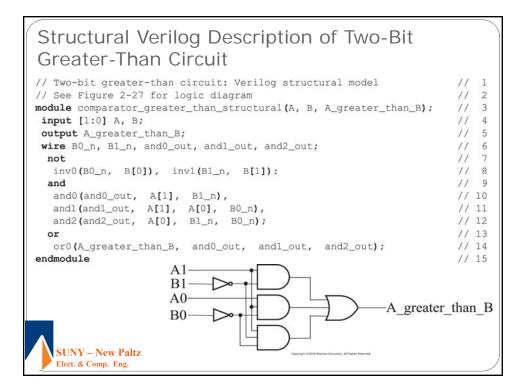

| Testbench for the Structural Model                                  | l of the |

|---------------------------------------------------------------------|----------|

| Two Dit Creator Than Comparator                                     |          |

| Two-Bit Greater-Than Comparator                                     |          |

| // Testbench for Verilog two-bit greater-than comparator            | // 1     |

| <pre>module comparator_testbench_verilog();</pre>                   | // 2     |

| reg [1:0] A, B;                                                     | // 3     |

| wire struct_out;                                                    | // 4     |

| <pre>comparator_greater_than_structural U1(A, B, struct_out);</pre> | // 5     |

| initial                                                             | // 6     |

| begin                                                               | // 7     |

| A = 2'bl0;                                                          | // 8     |

| B = 2'b00;                                                          | // 9     |

| #10;                                                                | // 10    |

| B = 2'b01;                                                          | // 11    |

| #10;                                                                | // 12    |

| B = 2'b10;                                                          | // 13    |

| #10;                                                                | // 14    |

| B = 2'b11;                                                          | // 15    |

| end                                                                 | // 16    |

| endmodule                                                           | // 17    |

| Copyright ©2016 Pearson Education, AII Rights Reserved              |          |

|                                                                     |          |

|                                                                     |          |

| SUNY – New Paltz                                                    |          |

| Elect. & Comp. Eng.                                                 |          |

| Arithmetic in Verilog                                |  |

|------------------------------------------------------|--|

| module Arithmetic (A, B, Y1, Y2, Y3, Y4, Y5);        |  |

| <b>input</b> [2:0] A, B;                             |  |

| <b>output</b> [3:0]Y1;                               |  |

| <b>output</b> [4:0]Y3;                               |  |

| output [2:0]Y2,Y4,Y5;                                |  |

| reg [3:0]Y1;                                         |  |

| reg [4:0]Y3;                                         |  |

| reg [2:0]Y2,Y4,Y5;                                   |  |

| always @(A or B)                                     |  |

| begin                                                |  |

| Y1=A+B;//addition                                    |  |

| Y2=A-B;//subtraction                                 |  |

| Y3=A*B;//multiplication                              |  |

| Y4=A/B;//division                                    |  |

| Y5=A%B;//modulus of A divided by B                   |  |

| end                                                  |  |

| endmodule<br>SUNY – New Paltz<br>Elect. & Comp. Eng. |  |

| Equality and inequality Operations in Verilog<br>module Equality (A, B,Y1,Y2,Y3); |

|-----------------------------------------------------------------------------------|

| input [2:0] A, B;                                                                 |

| output Y1,Y2;                                                                     |

| output [2:0]Y3;                                                                   |

| reg Y1,Y2;                                                                        |

| reg [2:0]Y3;                                                                      |

|                                                                                   |

| always @(A or B)                                                                  |

| begin                                                                             |

| Y1=A==B;//Y1=1 if A equivalent to B                                               |

| Y2=A!=B;//Y2=1 if A not equivalent to B                                           |

| if (A==B)//parenthesis needed                                                     |

| Y3=A;                                                                             |

| else                                                                              |

| Y3=B;                                                                             |

| end                                                                               |

| endmodule<br>SUNY – New Paltz<br>Elect. & Comp. Eng.                              |

| Logical Operations in Verilog                               |  |

|-------------------------------------------------------------|--|

| <b>module</b> Logical (A, B, C, D, E, F,Y);                 |  |

| input [2:0] A, B, C, D, E, F;                               |  |

| output Y;                                                   |  |

| reg Y;                                                      |  |

| always @(A or B or C or D or E or F)                        |  |

| begin                                                       |  |

| if ((A==B) && ((C>D)     !(E <f)))< td=""><td></td></f)))<> |  |

| Y=1;                                                        |  |

| else                                                        |  |

| Y=0;                                                        |  |

| end                                                         |  |

| endmodule                                                   |  |

|                                                             |  |

|                                                             |  |

| SUNY – New Paltz                                            |  |

| Elect. & Comp. Eng.                                         |  |

| Pit wice One                                         | rationa in Varilad               |

|------------------------------------------------------|----------------------------------|

| BIL-WISE Ope                                         | rations in Verilog               |

| module Bitwise (                                     | (A, B, Y);                       |

| input                                                | [6:0] A;                         |

| input                                                | 5:0] B;                          |

| output                                               | t [6:0]Y;                        |

| reg [6:                                              | D]Y;                             |

| alway                                                | s@(A or B)                       |

| begin                                                |                                  |

|                                                      | Y[0]=A[0]&B[0]; //binary AND     |

|                                                      | Y[1]=A[1] B[1]; //binary OR      |

|                                                      | Y[2]=!(A[2]&B[2]); //negated AND |

|                                                      | Y[3]=!(A[3] B[3]); //negated OR  |

|                                                      | Y[4]=A[4]^B[4]; //binary XOR     |

|                                                      | Y[5]=A[5]~^B[5]; //binary XNOR   |

|                                                      | Y[6]=!A[6]; //unary negation     |

| end                                                  |                                  |

| endmodule<br>SUNY – New Paltz<br>Elect. & Comp. Eng. |                                  |

| Shift Operations in Verilog                                 |  |

|-------------------------------------------------------------|--|

| module Shift (A,Y1,Y2);                                     |  |

| input [7:0] A;                                              |  |

| <b>output</b> [7:0]Y1,Y2;                                   |  |

| <b>parameter</b> B=3; reg [7:0]Y1,Y2;                       |  |

| always @(A)                                                 |  |

| begin                                                       |  |

| Y1=A< <b; left<="" logical="" shift="" td=""><td></td></b;> |  |

| Y2=A>>B; //logical shift right                              |  |

| end                                                         |  |

| endmodule                                                   |  |

|                                                             |  |

|                                                             |  |

|                                                             |  |

|                                                             |  |

| SUNY – New Paltz<br>Elect. & Comp. Eng.                     |  |